# STM32 PMSM SDK 5.2 training

T.O.M.A.S. team

#### Peripherals for advanced motor control Overview

#### Peripherals for advanced motor control

#### PWM generation

- Speed / position feedback

- Multi timer configuration

- Analog to Digital converter

- Other inbuilt peripherals (DMA, connectivity)

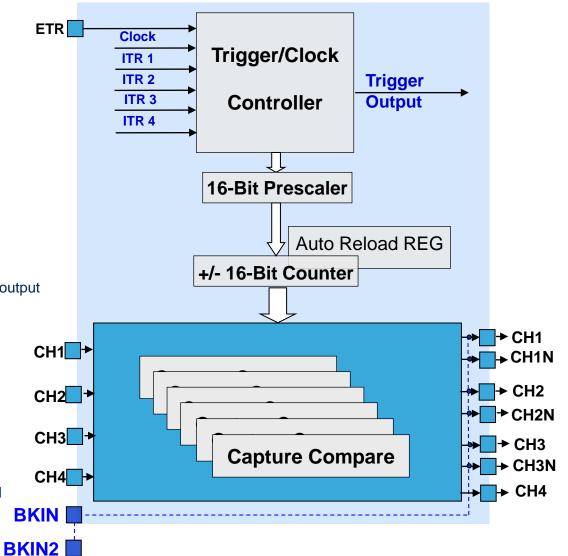

#### Advanced timer Features overview

- TIM1, 8 (,20) on High Speed APB (APB2)

- Internal clock up to 144 MHz

- 16-bit Counter

- Up, down and centered counting modes

- Auto Reload

- 4 (6) x 16-bit Capture Channels

- Output Compare

- PWM

- Input Capture, PWM input Capture

- One Pulse Mode

- 6 Complementary outputs: Channel1, 2 and 3

- Output Idle state selection independent for each output

- Polarity selection independent for each output

- Programmable PWM repetition counter

- Hall sensor interface

- Encoder interface

- 8 Independent IRQ/DMA Requests Generation

- Embedded Safety features

- Break inputs

- Lockable unit configuration: 3 possible Lock level

- The PWM mode allows to generate:

- 7 independent signals for TIM1 and TIM8 (TIM20)

- 4 independent signals for TIM2, 3 and 4

- Max input clock is 72MHz to provide 13.8ns edge resolution (12-bit @16kHz edge-aligned PWM) •

- The frequency and a duty cycle determined as follow: •

- One auto-reload register to defined the PWM period. .

- Each PWM channel has a Capture Compare register to define the duty cycle.

- → Example: to generate a 40 KHz PWM signal w/ duty cycle of 50% on TIM1 clock at 72MHz:

- Load Prescaler register with 0 (counter clocked by TIM1CLK/(0+1)), Auto Reload register with 1799 and CCRx register with 899

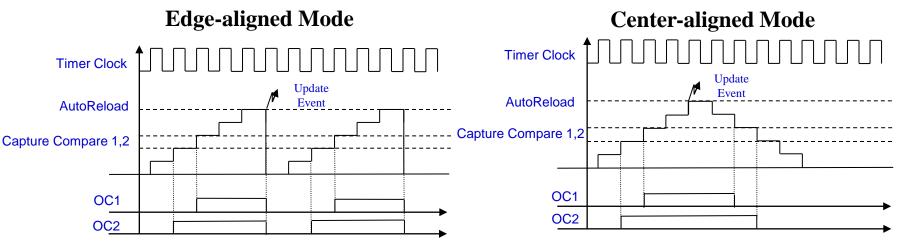

- There are two configurable PWM modes:

#### PWM Mode

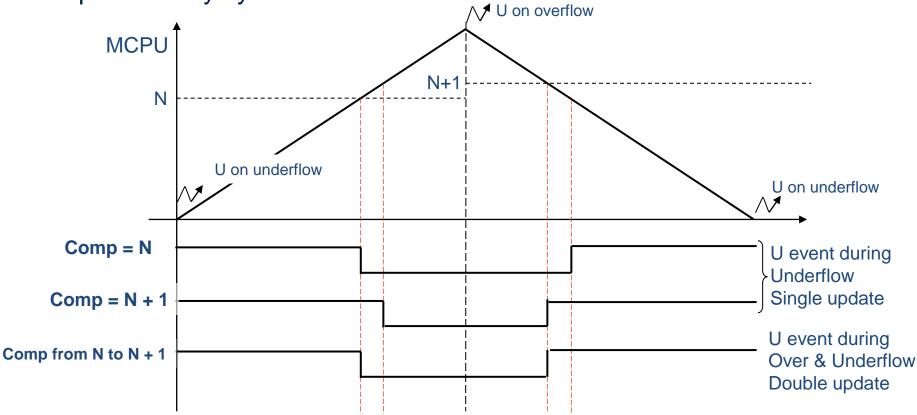

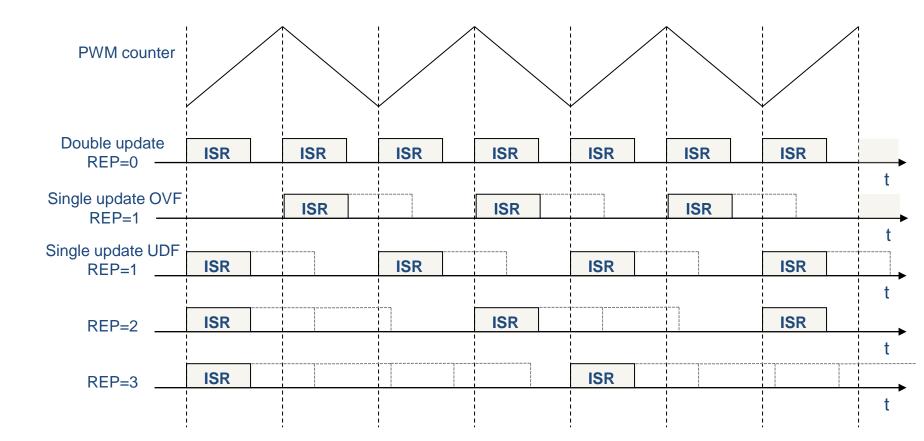

#### Double Update Mode

• An Update event (U) during the Overflow of the PWM counter improves duty cycle resolution.

#### PWM main Interrupt Service Routine 7

- So-called U (Update) event

- · Synchronously transfers all preload into active registers

- 3 (4) compares for duty cycles

- Preload mechanism can be disabled if needed

- 1 Auto Reload for PWM switching period

- allows changing on-the-fly the PWM frequency while maintaining duty cycles

- PWM clock prescaler

- Adjustable U event rate

- programmable through a 8-bit repetition counter

- Allows to choose Overflow/Underflow or both for update

#### **Repetition Counter**

#### Other interrupts and DMA

- Other interrupt sources available on PWM timer

- Each Compare match (up or down counting selectable) or capture •

- Trigger events

- **Emergency Stop** •

- Some events are also mapped on the DMA controller

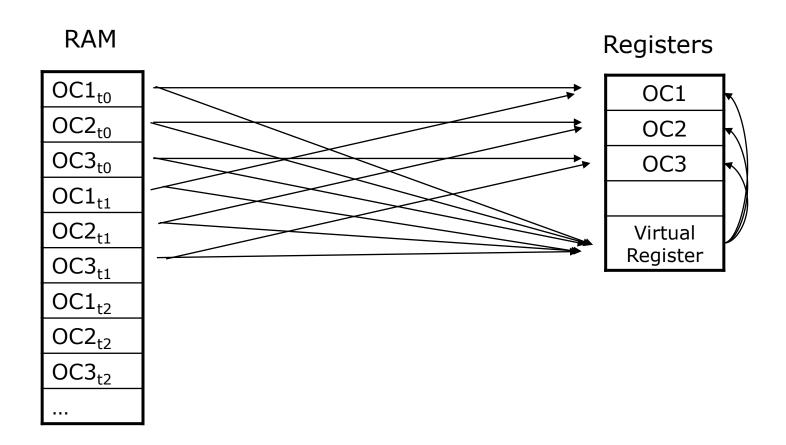

#### PWM's DMA burst transfer

• Allows to update several registers with a single DMA event

• Efficient use of DMA (a single stream is required)

#### PWM outputs management 11

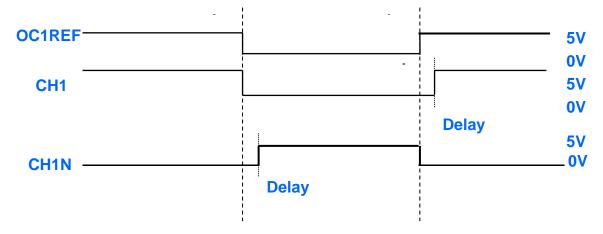

- Programmable hardware deadtime generation

- 8-bit register with 13.8ns max resolution at 72MHz (from 0 to 14µs, nonlinear)

Internal PWM before dead time generator High side PWM

Low side PWM

- Individually selectable polarity selection

- Dedicated emergency stop input

- Shuts down the 6 PWM outputs and issues an interrupt

- Asynchronous operation (operates without clock source)

### Versatile PWM redirection circuitry

| Table                 |             |             |             | or com       | plementary OCX and OCXN                           |                                                              | 1                                                     |  |  |  |

|-----------------------|-------------|-------------|-------------|--------------|---------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------|--|--|--|

| Control Bits          |             |             |             |              | Outpu                                             | ut State                                                     |                                                       |  |  |  |

| MOE<br>bit            | OSSI<br>bit | OSSR<br>bit | OCxE<br>bit | OCxNE<br>bit | OCx output state                                  | OCxN output state                                            |                                                       |  |  |  |

| -<br>-<br>-<br>-<br>- | х           | 0           | 0           | 0            | Output disabled                                   | Output disabled                                              | 1_                                                    |  |  |  |

|                       | x           | 0           | 0           | 1            | Output disabled                                   | OCREF + Polarity<br>(OCREF xor OCxP)                         | PWM timer used as a                                   |  |  |  |

|                       | x           | 0           | 1           | 0            | OCREF + Polarity<br>(OCREF xor OCxP)              | Output disabled                                              | GP timer<br>Motor Control (sinewave)<br>Motor Control |  |  |  |

|                       | x           | 0           | 1           | 1            | OCREF + Polarity + dead-<br>time                  | Complementary to OCREF (not<br>OCREF) + Polarity + dead-time |                                                       |  |  |  |

|                       | x           | 1           | 0           | 0            | Off-State (output enabled with<br>inactive state) | Off-State (cutput enabled with<br>inactive state)            |                                                       |  |  |  |

|                       | x           | 1           | 0           | 1            | Off-State (output enabled with<br>inactive state) | OCREF + Polarity<br>(OCREF xor OCxNP)                        | (6-steps)                                             |  |  |  |

|                       | x           | 1           | 1           | 0            | OCREF + Polarity<br>(OCREF xor OCxP)              | Off-State (output enabled with<br>inactive state)            |                                                       |  |  |  |

|                       | x           | 1           | 1           | 1            | OCREF + Polarity + dead-<br>time                  | Complementary to OCREF (not<br>OCREF) + Polarity + dead-time | <ul> <li>Motor Control (sinewave)</li> </ul>          |  |  |  |

|                       | 0           | х           | 0           | 0            |                                                   |                                                              | Outputs                                               |  |  |  |

|                       | 0           | х           | 0           | 1            | Outruit                                           | disabled                                                     | disconnected from                                     |  |  |  |

| 0.                    | 0           | х           | 1           | 0            | Culput                                            | aloublea                                                     |                                                       |  |  |  |

|                       | 0           | х           | 1           | 1            |                                                   |                                                              | I/O ports                                             |  |  |  |

|                       | 1           | х           | 0           | 0            |                                                   |                                                              |                                                       |  |  |  |

|                       | 1           | х           | 0           | 1            | Off-State (output enal                            | bled with inactive state)                                    | ← All PWMs OFF (low Z                                 |  |  |  |

|                       | 1           | х           | 1           | 0            | on orace (output end                              | and mar material or and                                      | for safe stop)                                        |  |  |  |

|                       | 1           | х           | 1           | 1            |                                                   |                                                              |                                                       |  |  |  |

#### Versatile PWM redirection circuitry

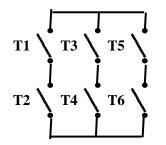

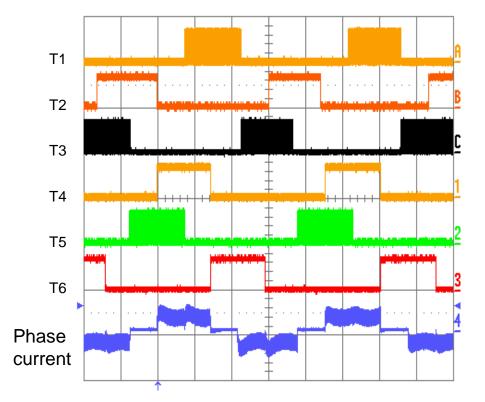

Example: 6-steps (or block commutated) drives

| Step | High | Low | OC1    | OC1N | OC2    | OC2N | OC3   | OC3N |

|------|------|-----|--------|------|--------|------|-------|------|

| 1    | T1   | T4  | oc1ref | 0    | 0      | 1    | 0     | 0    |

| 2    | T1   | T6  | oc1ref | 0    | 0      | 0    | 0     | 1    |

| 3    | T3   | T6  | 0      | 0    | oc2ref | 0    | 0     | 1    |

| 4    | T3   | T2  | 0      | 1    | oc2ref | 0    | 0     | 0    |

| 5    | T5   | T2  | 0      | 1    | 0      | 0    | oc3re | f 0  |

| 6    | T5   | T4  | 0      | 0    | 0      | 0    | oc3re | f 0  |

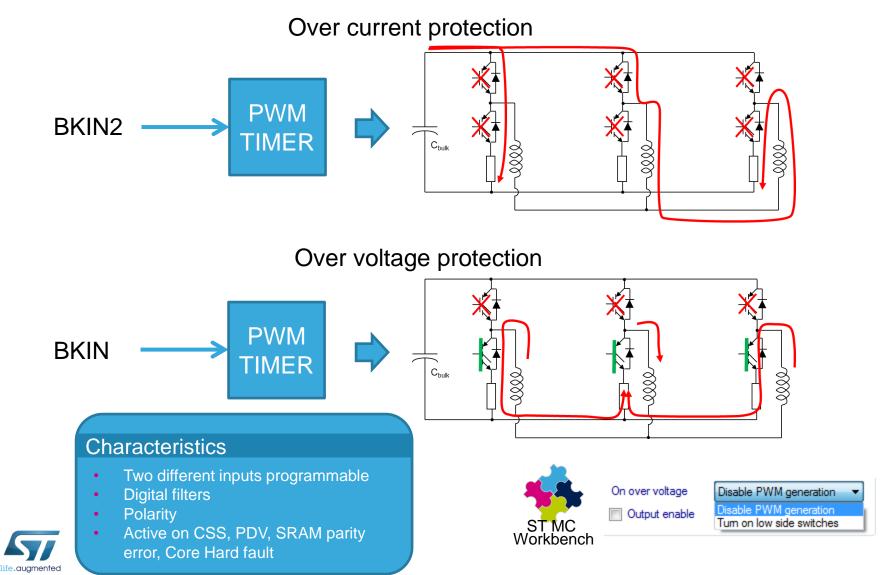

#### Break input 14

- A break event can be generated by:

- The BRK input which has a programmable polarity and an enable bit BKE

- The Clock Security System

- When a break occurs:

- The MOE bit (Main Output Enable) is cleared

- The break status flag is set and an interrupt request can be generated

- Each output channel is driven with the level programmed in the OISx bit

- Break applications:

- If the AOE is Reset, the MOE remains low until you write it to '1' again

- Normally used for security with break input connected to an alarm feedback from power stage, thermal sensors or any security components.

- If the AOE (Automatic Output Enable) bit is set, the MOE bit is automatically set again at the next update event UEV

- Typically be used for cycle-by-cycle current regulation

#### Smoke inhibit protections 15

- Safety critical registers can be "locked", to prevent power stage damages (software run-away,...)

- Dead time, PWM outputs polarity, emergency input enable,...

- All target registers are read/write until lock activation (and then readonly if protected)

- Once the two lock bits are written, they cannot be modified until next MCU reset (write-once bits)

- Three programmable write protection levels

- Level1: Dead Time and Emergency enable are locked.

- Level2: Level1 + Polarities and Off-state selection for run and Idle state are locked.

- Level3: Level2 + Output Compare Control and Preload are locked.

- GPIO configuration can be locked to avoid having the PWM alternate function outputs reprogrammed as standard outputs

#### Debug feature 16

- Motor control applications are usually tricky to debug using breakpoints

- Standard breakpoints may damage the power stage

- Closed loop systems can hardly be stopped and re-started

- A configuration bit allows to program the behavior of the PWM timer upon breakpoint match

- Normal mode: the timer continues to operate normally

- May be dangerous in some case since a constant duty cycle is applied to the inverter (interrupts not serviced)

- Safe mode: the timer is frozen and PWM outputs are shut down

- Safe state for the inverter. The timer can still be re-started from where it stops.

#### Peripherals for advanced motor control

- PWM generation

- Speed / position feedback

- Multi timer configuration

- Analog to Digital converter

- Other inbuilt peripherals (DMA, connectivity)

#### Speed Feedback 18

- Handled by the general purpose timers in dedicated modes

- These functions are available on most timers

- Hall sensors

- Hall Sensor interface (XOR'ed inputs)

- Encoder

- Encoder modes 1, 2 & 3 (2x, 4x)

- Tacho feedback

- Clear on capture to measure exact period

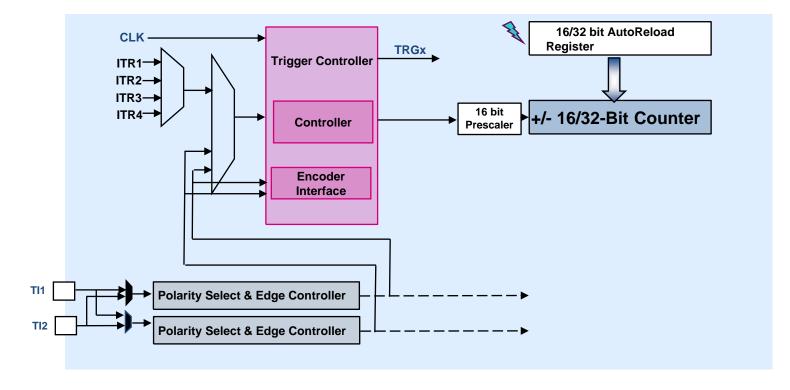

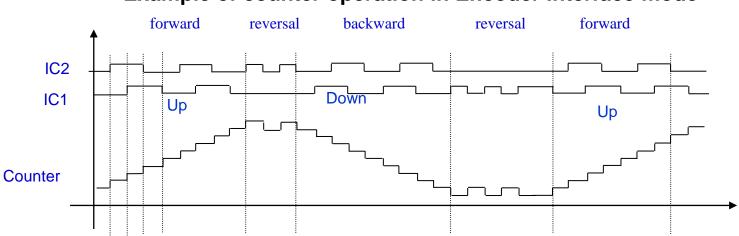

#### TIM Block Diagram in encoder mode

#### Interfacing a TIM timer with an encoder

- Encoders and STM32 connection example:

- An incremental encoder can be connected directly to the MCU without external interface logic.

- The third encoder output which indicates the mechanical zero position (Z or index), may be connected to an external interrupt and trigger a counter reset

#### Key encoder features 21

- Programmable counting rate

- x4: normal mode, all edges active

- a 1000 lines encoder will give 4000 counts per revolution

- x2: counts on input A (or B) only, but direction still determined with A and B

- "velocity mode": encoder clock can be further prescaled if needed

- Programmable encoder resolution

- When programming the autoreload register with the number of counts per revolution, the counter register directly holds the angle or the position

- No need to do the difference vs previous counter value

- If set to 0xFFFF, can be made compatible with previous designs using a freerunning counter

- Possibility to generate one/multiple interrupts per revolution:

- once every 360°

- once 60°, 90°,... (depending on autoreload register setting)

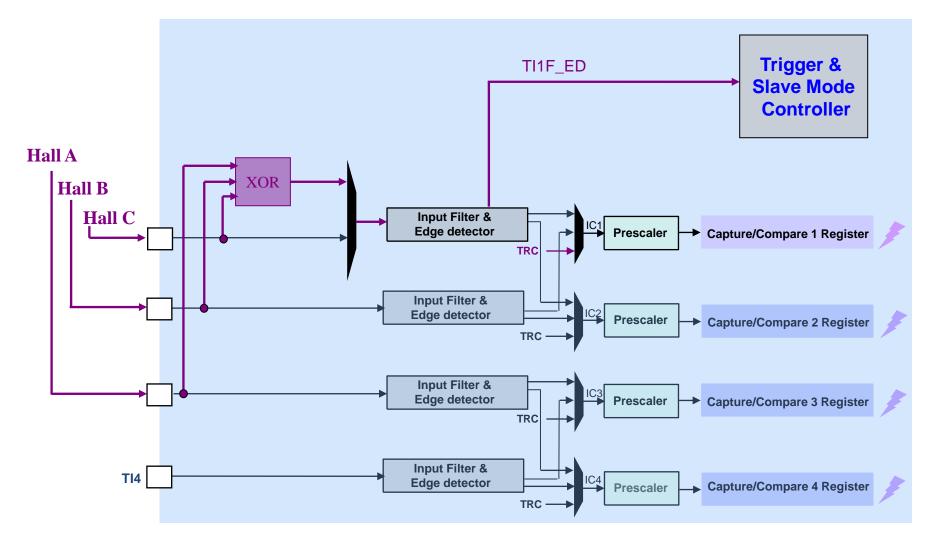

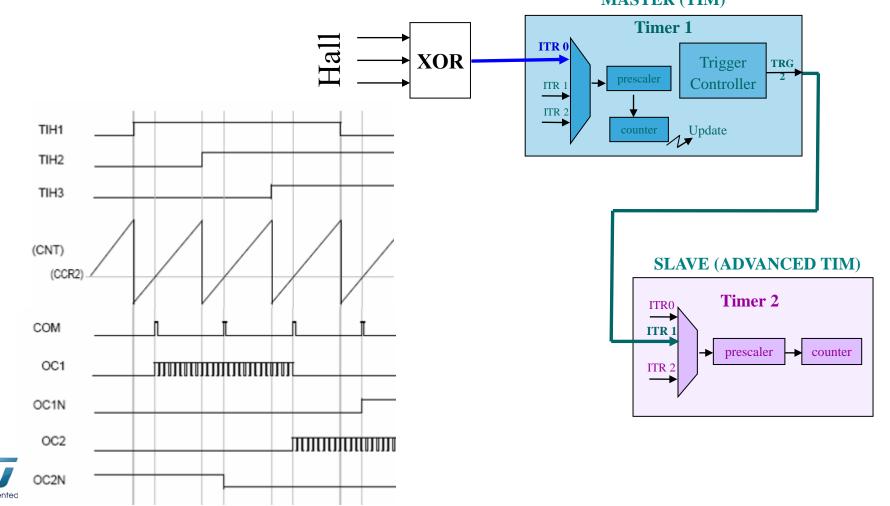

#### Hall sensor Interface 22

#### Peripherals for advanced motor control<sup>23</sup>

- PWM generation

- Speed / position feedback

- Multi timer configuration

- Analog to Digital converter

- Other inbuilt peripherals (DMA, connectivity)

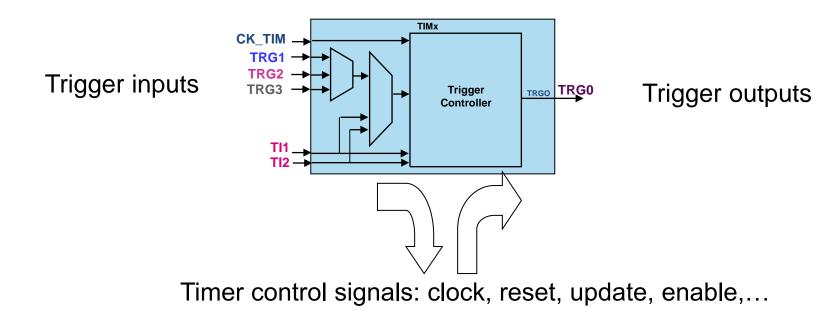

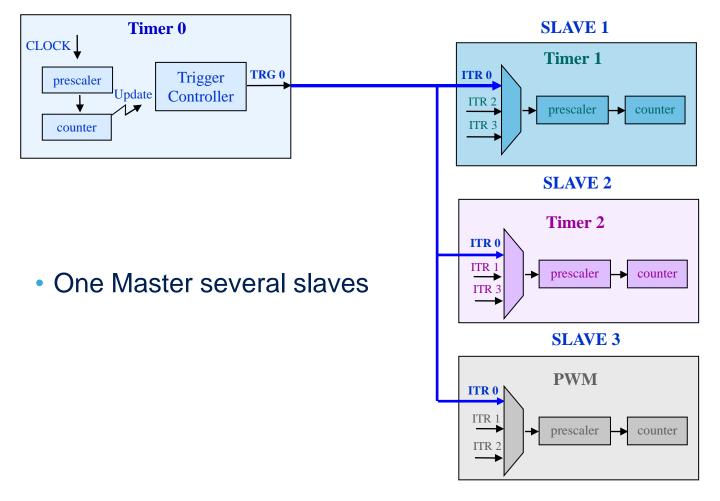

#### Timer Link system 24

- The three general purpose and the advanced timers are linked together and can be synchronized or chained, thanks to a Trigger output and several selectable trigger inputs.

- For TIM2:0, the input pins(TI1 and TI2) can also be used as triggers

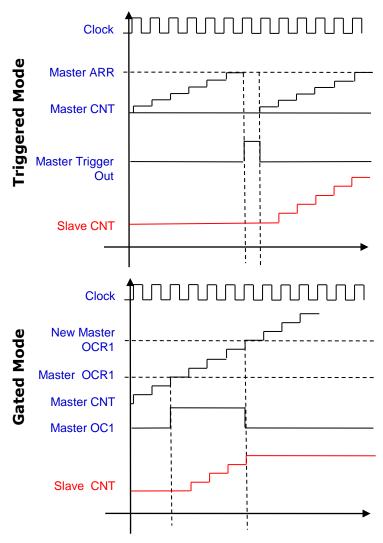

### Synchronization Mode Configuration

- When in **master** mode, the timer can output one of these:

- Counter reset

- Counter enable

- Update event

- Output Compare signal

- When configured as slave, the timer can work in the following modes:

- Triggered

- Gated

- Reset

- External clock

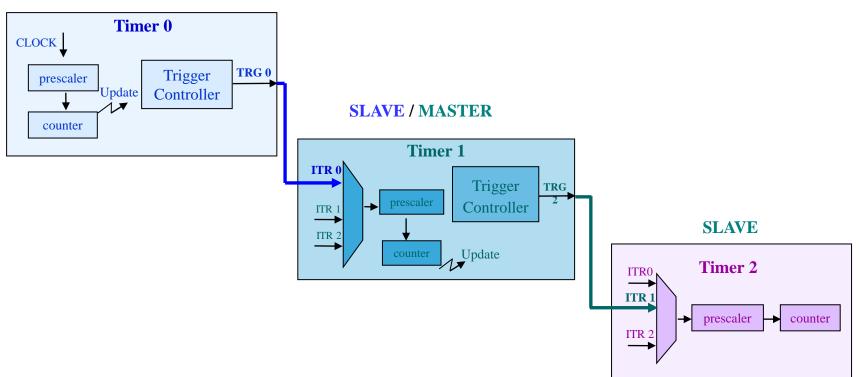

#### Example 1/3: chained timers 26

Cascade mode (for instance, chained time bases)

#### **MASTER**

#### Examples 2/3: synchronized start 27

MASTER

#### Examples 3/3: block commutation 28

A TIM timer handles Hall feedback and triggers an advanced timer for step commutation

MASTER (TIM)

#### Peripherals for advanced motor control 29

- PWM generation

- Speed / position feedback

- Multi timer configuration

- Analog to Digital converter

- Other inbuilt peripherals (DMA, connectivity)

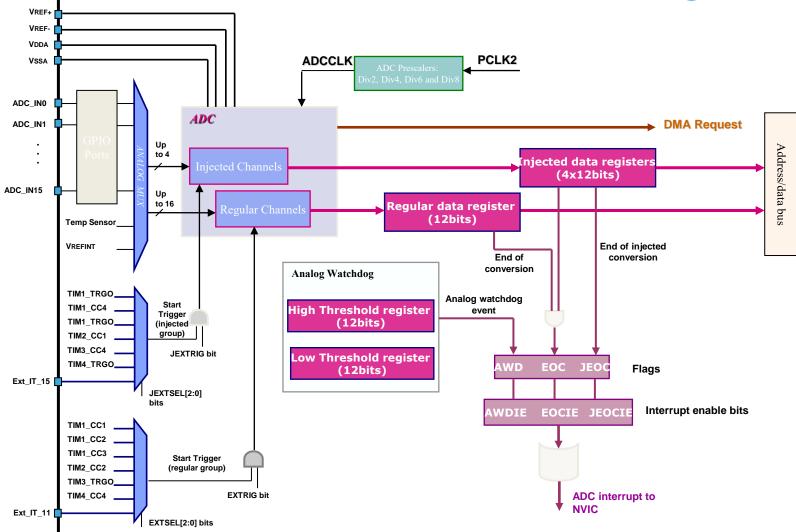

# ADC Features (1/3) 30

- ADC conversion rate 1 MHz and 12-bit resolution

- 1µs conversion time at 56 MHz ٠

- 1.17µs conversion time at 72 MHz ٠

- Conversion range: 0 to 3.6 V ٠

- ADC supply requirement: 2.4V to 3.6 V

- ADC input range: VREF- ≤ VIN ≤ VREF+ (VREF+ and VREF- available only in LQFP100 package)

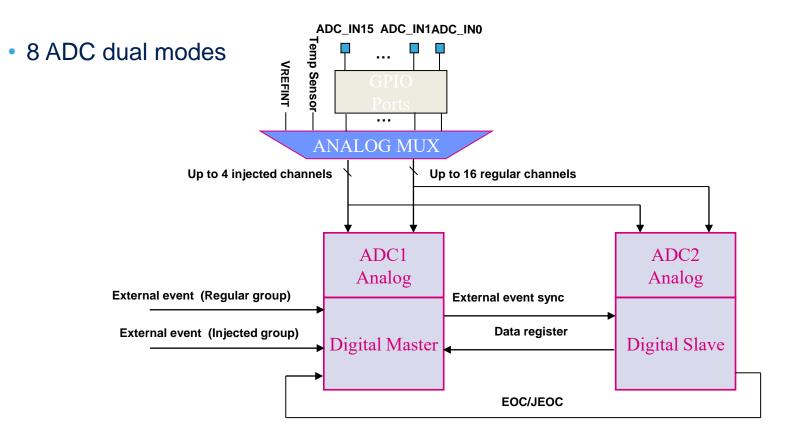

- Dual mode (on devices with 2 ADCs): 8 conversion mode •

- Up to 18 multiplexed channels:

- 16 external channels

- 2 internal channels: connected to Temperature sensor and internal reference voltage (VREFINT=1.2V)

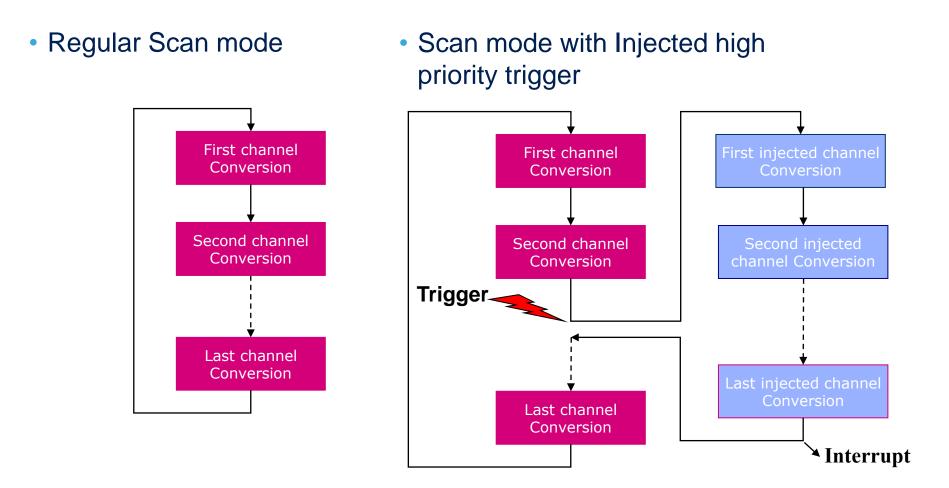

- Channels conversion groups:

- Up to 16 channels regular group

- Up to 4 channels injected group

- Single and continuous conversion modes

#### **ADC Injected Conversion**

# ADC Features (2/3) 32

- Analog Watchdog(s) (1 channel or all regular or all injected) •

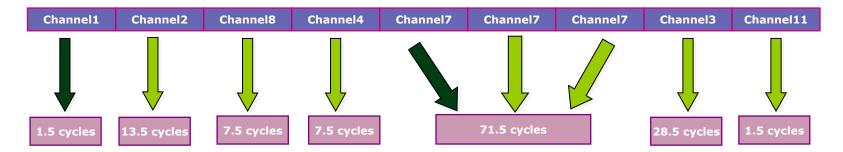

- Sequencer-based scan mode •

- Any channel, any order (e.g. Ch3, Ch2, Ch11, Ch11, Ch3) •

- up to 16 regular conversion (transferred by DMA) ٠

- up to 4 injected conversion stored in internal registers

- Multiple trigger sources for both regular and injected conversion

- Each group can be started by 6 events from the 4 timers (compare, over/underflow) •

- External event and software trig also available •

### ADC Features (3/3)

- Left or right Data alignment with built-in data coherency

- 4 offset compensation registers

- Compensates external conditioning components offsets (such as Operational Amplifiers). Provides signed results if needed.

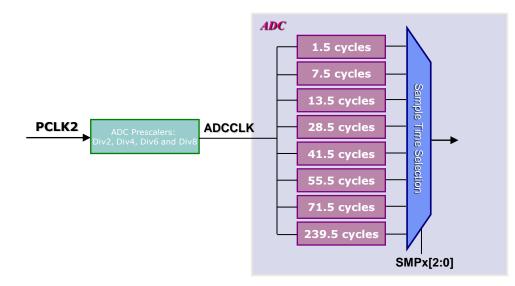

- Channel-by-channel programmable sampling time to be able to convert signals with ٠ various impedances

- From 1 $\mu$ s (for Rin < 1.2 kOhm) to 18 $\mu$ s (Rin < 350 kOhm), 8 values

#### ADC Block Diagram 34

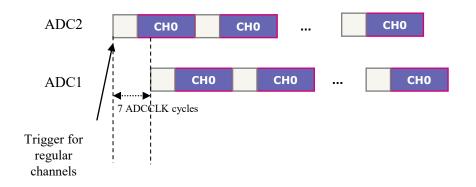

#### ADC dual modes (1/2)

- Available in devices with two ADCs (Performance line)

- ADC1 and ADC 2 can work independently or coupled (master/slave)

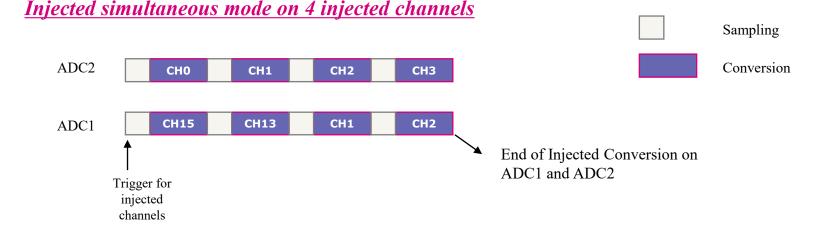

#### ADC dual modes example (2/2)

#### Fast Interleaved mode on 1 regular channel in continuous conversion mode

#### Up to 2 MSps data throughput (DMA-based)

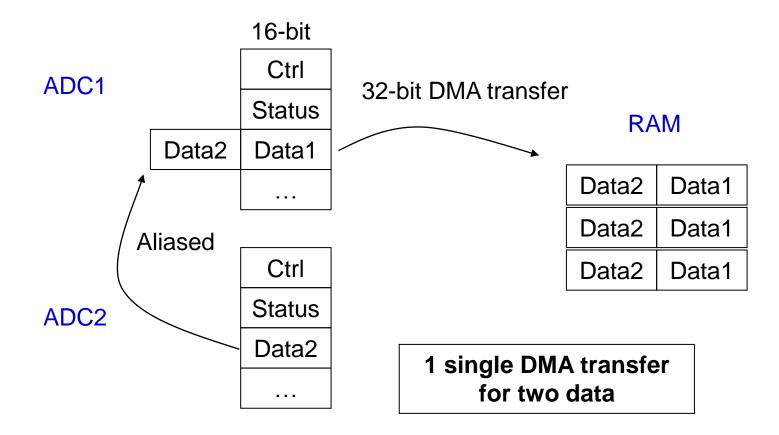

#### DMA transfers in interleaved mode

Interleaved mode: continuous conversions of the two ADCs on the same channel with aliased data register

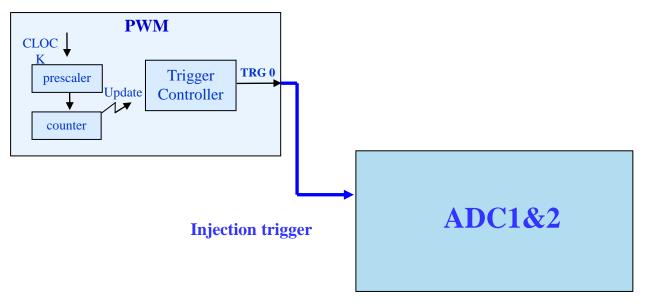

### ADC synchronization in STM32

- Done thanks to a synchronization unit embedded in the PWM timer. •

- 2 options available:

- Direct synchronization on PWM crest, valley, or both.

- Delayed synchronization with the 4<sup>th</sup> Compare channel

- The ADC results can be then processed with an end of conversion interrupt or transferred by DMA.

#### Direct synchronization 39

- The PWM timer "update" signal triggers Simultaneous injected conversions on both ADCs

- No error due to sequential phase sampling

#### **MASTER**

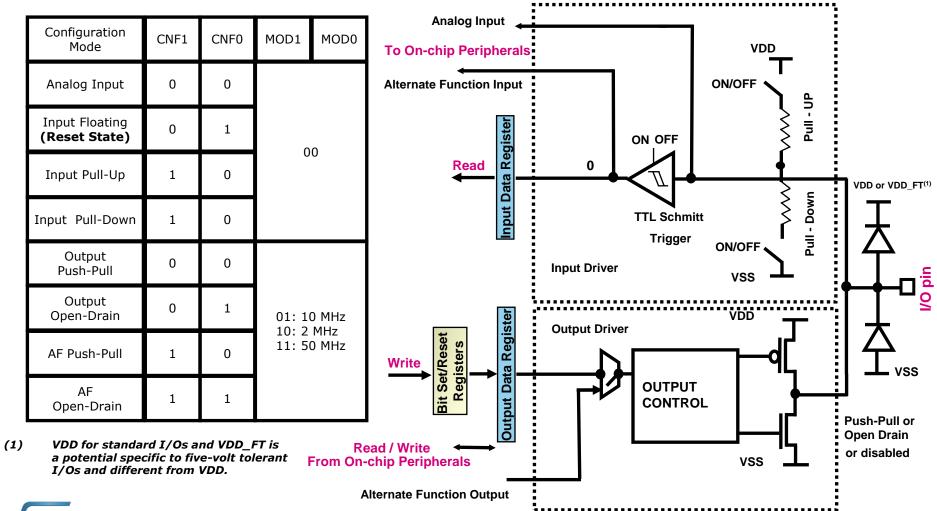

## **GPIO Features**

#### GPIO Features 41

- Up to 80 multifunction bi-directional I/O ports available: 80% IO ratio

- Standard I/Os 5V tolerant

- The GPIOs can sink or source 25mA (total currents sunk is 150mA) •

- 36-42 MHz Toggling

- Configurable Output Speed up to 50 MHz ٠

- Up to 24 Analog Inputs

- Alternate Functions pins (like USARTx, TIMx, I2Cx, SPIx, CAN, USB...)

- All GPIOs can be set-up as external interrupt (up to 16 lines at time)

- 1-4 I/Os can be used as Wake-Up from STANDBY (PA0) ٠

- One I/O can be set-up as Tamper Pin (PC13)

- All Standard I/Os are shared in ports (GPIOA..GPIOF)

- Atomic Bit Set and Bit Reset using BSRR and BRR registers

- Locking mechanism to avoid spurious write in the IO registers

- When the LOCK sequence has been applied on a port bit, it is no longer possible to modify the configuration of the port bit until the next reset (no write access to the CRL and CRH registers corresponding bit).

(84 MHz / 90 MHz / 100 MHz)

(84 MHz / 90 MHz / 100 MHz)

### GPIO Configuration Modes 42

#### Peripherals for advanced motor control 43

- PWM generation

- Speed / position feedback

- Multi timer configuration

- Analog to Digital converter

- Other inbuilt peripherals (DMA, connectivity)

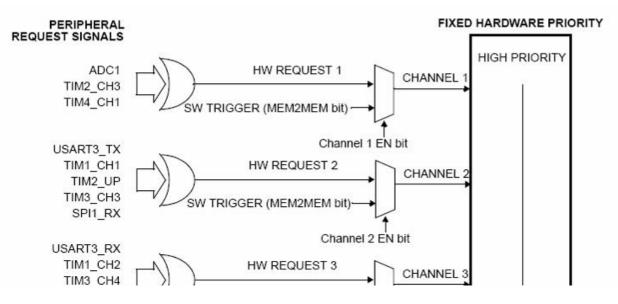

#### DMA & features

- Standalone data-transfer controller

- 5-16 independently configurable channels: hardware requests or software trigger on each channel

- Software programmable priorities: Very high, High, Medium or Low (Hardware priority in case of equality)

- Programmable and Independent source and destination transfer data size: • Byte, HalfWord or Word

- 3 event flags for each channel: DMA Half Transfer, DMA Transfer complete and DMA Transfer Error

- Memory-to-memory, peripheral-to-memory, memory-to-peripheral transfers and • peripheral-to-peripheral transfer types

- Faulty channel is automatically disabled in case of bus access error •

- Programmable number of data to be transferred: up to 2x 65535 •

- Support for circular buffer management and dual-buffer ٠

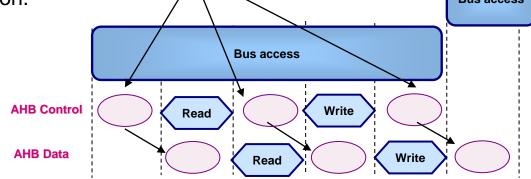

#### DMA and Bus occupation

- Request, arbitration and acknowledgement operations are done outside AHB system bus, so the bus is not occupied during those phases

- One DMA access takes 2 cycles (on AHB): the system bus can not be totally freeze by DMA as at least 3 cycles are left to the CPU during one DMA transaction.

Current DMA controller compared to others which permit burst transfer have nearly the same system bus occupation rate. However, it doesn't freeze the bus for many cycles consecutively as it is the case with the burst mode: better performance with many small data transfer without blocking the bus

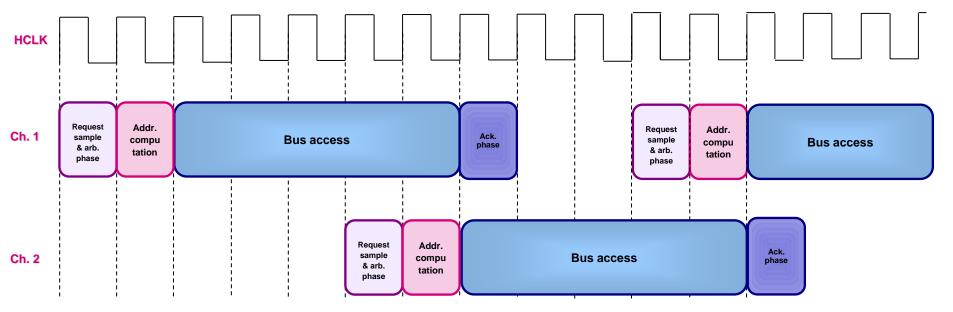

### DMA Latency: 2 transfers 46

To improve the DMA performances, a new request can be served while the previous one is running: if a • request is active and others are pending, the new request sample & arbitration phase is performed during AHB bus access of the current request. The winning request for AHB bus access will start immediately after the end of the current request's AHB Bus access.

• If source or destination is on APB, the transfer takes more cycles (1+N for APB:AHB = N:1)

- Different STM32 families are equipped with various communication peripherals and other interfaces:

- USART (up to 8x)

- SPI (up to 3x)

- CAN (up to 2x)

- Ethernet MAC

- USB OTG (up to 2x)

- I2C (up to 3x)

- I2S (2x), SAI

- SDIO

- Camera

- You can find more details in datasheet or dedicated training sessions

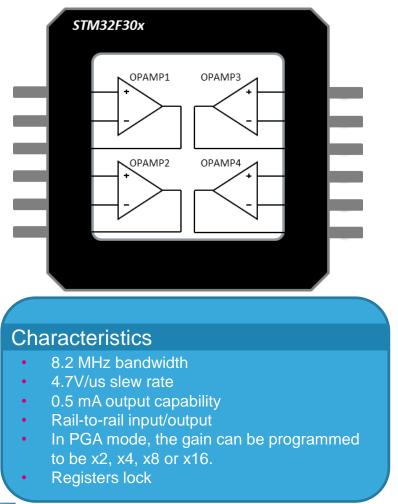

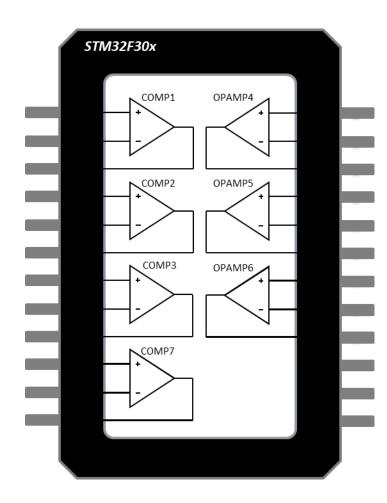

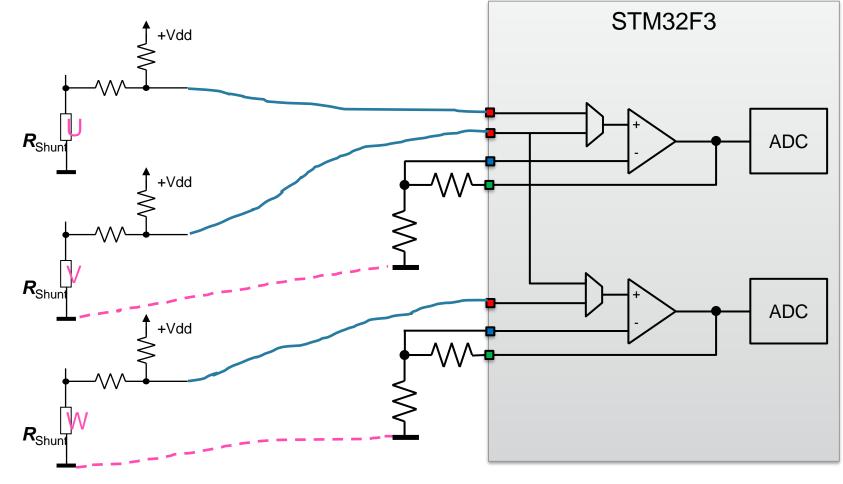

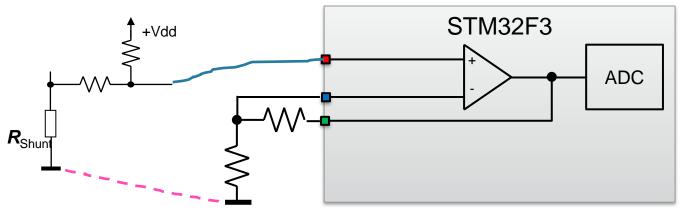

## STM32 F3 embedded analog

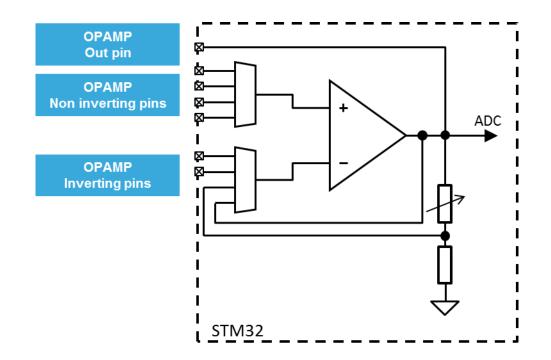

### **Operational amplifier**

Up to four embedded PGA for current sensing conditioning

life.auamented

#### Operational amplifiers 50

Available pins

| OPAMP1<br>Inverting pins | OPAMP1<br>Non inverting pins | OPAMP1<br>Out pin | OPAMP2<br>Inverting pins | OPAMP2<br>Non inverting pins | OPAMP2<br>Out pin |

|--------------------------|------------------------------|-------------------|--------------------------|------------------------------|-------------------|

| PA3, PC5                 | PA1, PA7, PA3, PA5           | PA2               | PA5, PC5                 | PA7, PB14, PB0, PD14         | PA6               |

| OPAMP3                   | OPAMP3                       | OPAMP3            | OPAMP4                   | OPAMP4                       | OPAMP4            |

| Inverting pins           | Non inverting pins           | Out pin           | Inverting pins           | Non inverting pins           | Out pin           |

### Operational amplifier 51

Allowed configurations

#### **Comparators**

#### Up to seven fast comparators for fault protection

#### Characteristics

- 90ns propagation delay

- Rail-to-rail

- External or internal reference (DAC, 1.2V, 0.9V, 0.6V, 0.3V)

- Triggers Timer break inputs

- Registers lock

## Emergency inputs

**Different behaviors**

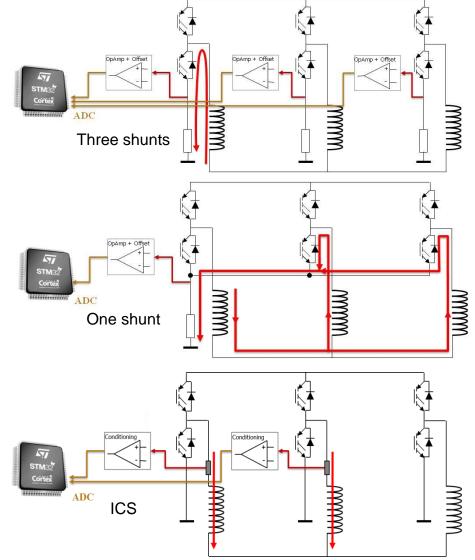

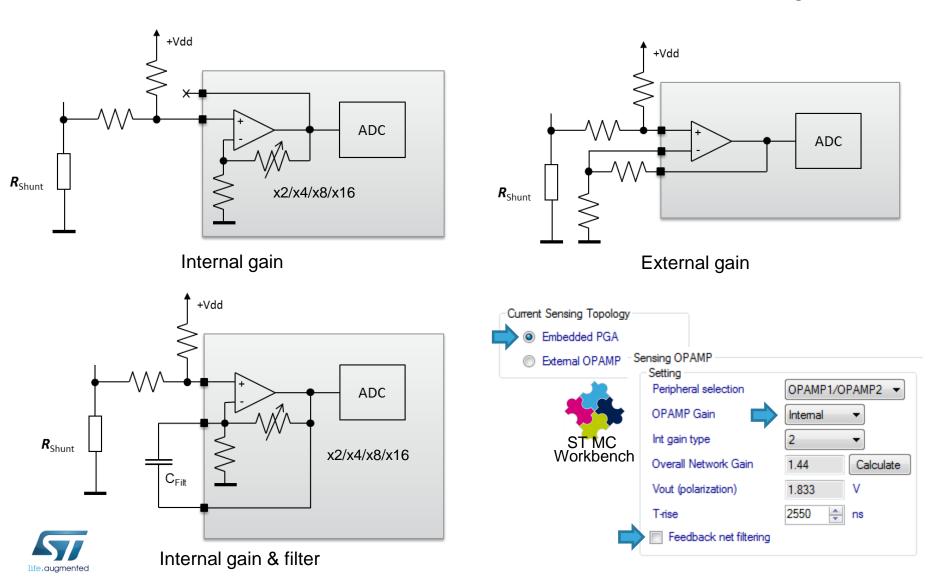

# MC library and Workbench support to F3 analog

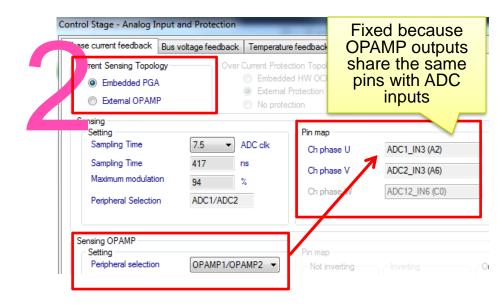

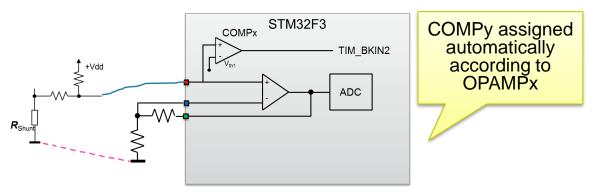

For a 3shunt current sensing topology, a new feature implemented in MC library v5.x allows to commit two F3's PGA instead of three as it's usual.

| Micro     | Available configurations   | or                         |

|-----------|----------------------------|----------------------------|

| STM32F303 | OPAMP1+ADC1<br>OPAMP2+ADC2 | OPAMP3+ADC3<br>OPAMP4+ADC4 |

| STM32F302 | OPAMP1+ADC1<br>OPAMP2+ADC2 |                            |

| Pow | er Stage - Current Sensing             |                       |

|-----|----------------------------------------|-----------------------|

|     | Lurrent sensor and signal conditioning |                       |

|     | Current reading topology               | Three Shunt Resistors |

|     | ICS gain                               | 1.000 × V/A           |

|     | Shunt resistor(s) value                | 0.220 💼 ohm           |

|     | Amplification on board                 |                       |

55

56

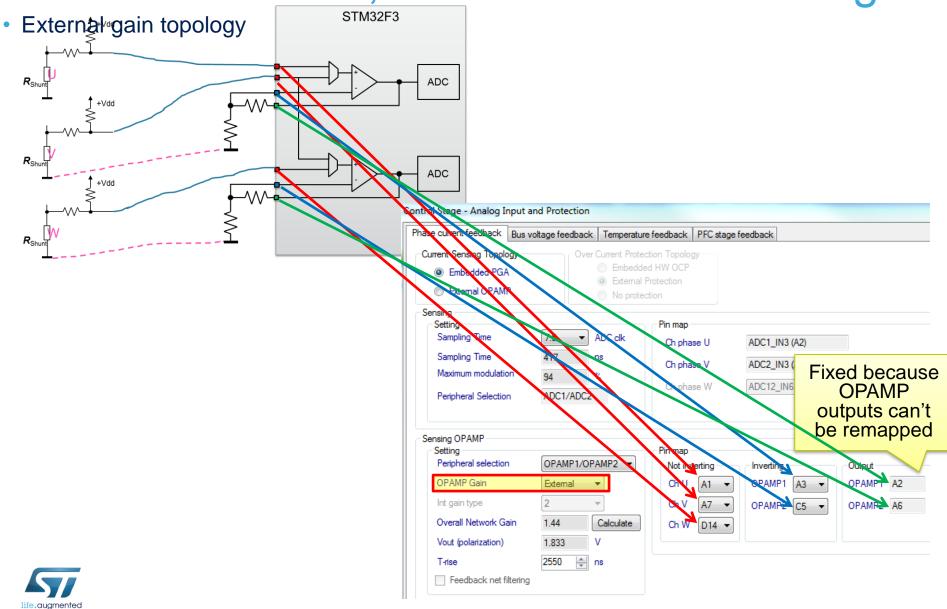

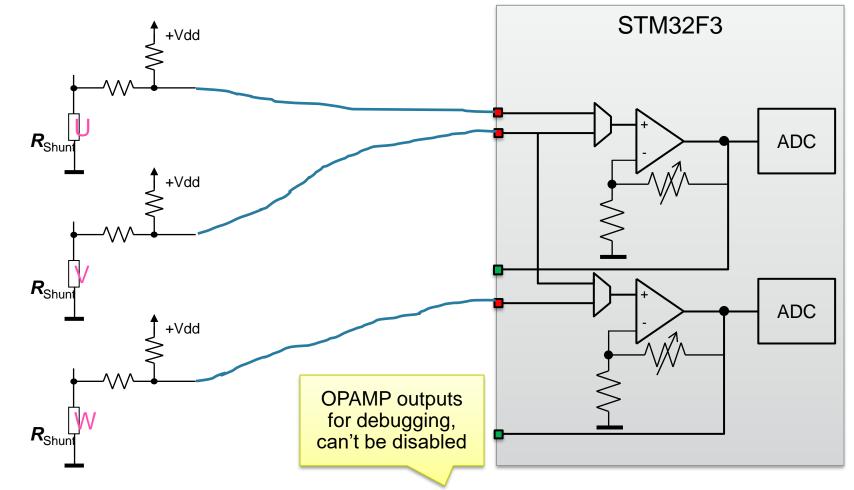

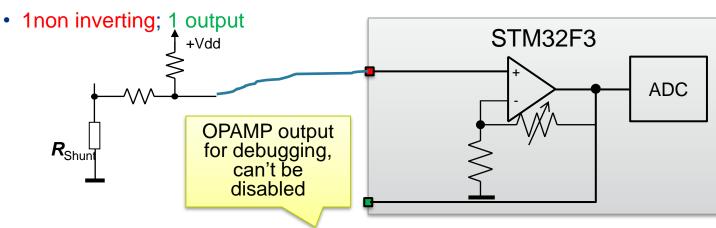

- External gain topology

- 7 mcu pins needed:

- 3 non inverting; 2 inverting; 2 output

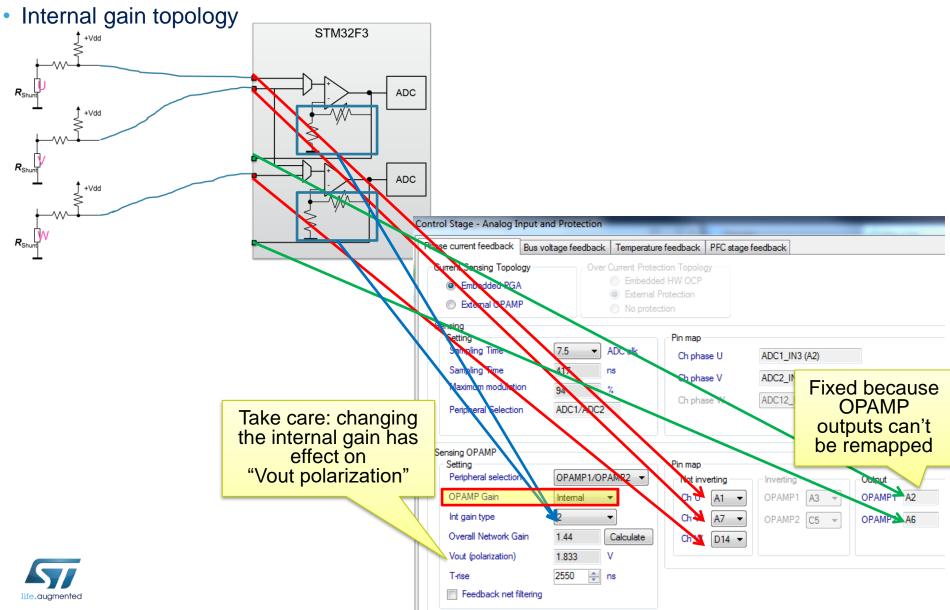

- Internal gain topology

- 5 mcu pins needed:

- 3 non inverting; 2 output

59

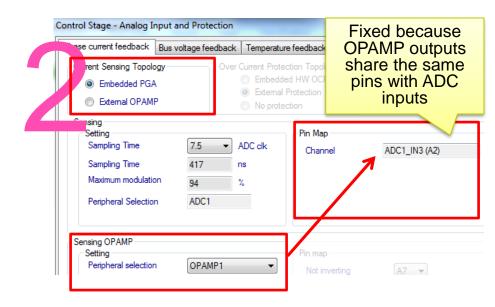

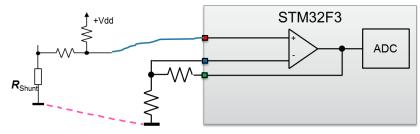

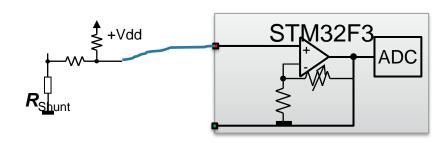

For a 1shunt current sensing topology, each one of the OPAMP/ADC structures can be selected

| Micro     | Available configurations | or          | or          | or          |

|-----------|--------------------------|-------------|-------------|-------------|

| STM32F303 | OPAMP1+ADC1              | OPAMP2+ADC2 | OPAMP3+ADC3 | OPAMP4+ADC4 |

| STM32F302 | OPAMP1+ADC1              | OPAMP2+ADC2 |             |             |

| P | owe | er Stage - Current Sensing             |                    |

|---|-----|----------------------------------------|--------------------|

|   |     | Current sensor and signal conditioning |                    |

|   |     | Current reading topology               | One Shunt Resistor |

|   |     | ICS gain                               | 1.000 × V/A        |

|   |     | Shunt resistor(s) value                | 0.220 🚖 ohm        |

|   |     | Amplification on board                 |                    |

60

Internal gain topology

- External gain topology3 mcu pins needed:

- - 1non inverting; 1 inverting; 1 output

2 mcu pins needed:

#### External gain topology

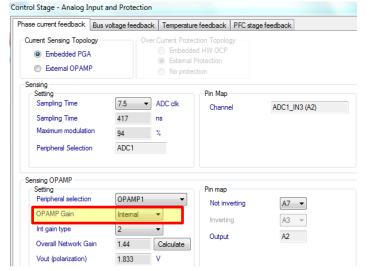

| rol Stage - Analog Ir           | nput and Protection  |                                                |                         |                 |             |

|---------------------------------|----------------------|------------------------------------------------|-------------------------|-----------------|-------------|

| ase current feedback            | Bus voltage feedback | Temperatu                                      | re feedback             | PFC stage feedb | ack         |

| urrent Sensing Topolo           | Over                 |                                                | ection Topolog          | JY              |             |

| Embedded PGA                    | <b>v</b>             |                                                | ed HW OCP<br>Protection |                 |             |

| External OPAMI                  | P                    | <ul> <li>External</li> <li>No prote</li> </ul> |                         |                 |             |

| ensing<br>Setting               |                      |                                                | Pin Map                 |                 |             |

| Sampling Time                   | 7.5 -                | ADC clk                                        | Channe                  | AD              | C1_IN3 (A2) |

| Sampling Time                   | 417                  | ns                                             |                         |                 |             |

| Maximum modulatio               | 94                   | %                                              |                         |                 |             |

| Peripheral Selection            | ADC1                 |                                                |                         |                 |             |

| ensing OPAMP                    |                      |                                                |                         |                 |             |

| Setting<br>Peripheral selection | OPAMP1               | •                                              | Pin map                 | (               |             |

| OPAMP Gain                      | External             |                                                | Not inv                 | erting          | A7 🔻        |

|                                 |                      |                                                | Invertin                | g (             | A3 🔻        |

| Int gain type                   | 2                    | <b>T</b>                                       | Output                  |                 | A2          |

| Overall Network Ga              | ain 1.44             | Calculate                                      |                         |                 |             |

| Vout (polarization)             | 1.833                | v                                              |                         |                 |             |

| T-rise                          | 2550 🚔               | ns                                             |                         |                 |             |

#### Internal gain topology

### PGA, dual motor control 63

- In a dual motor control project (STM32F303), all the configurations seen so far can be combined:

- 3shunt and 1shunt

- PGA and external OPAMP

- Embedded comparators and external comparators

#### • For instance, configurations can range from

| Motor        | Тороlоду | Resources for<br>current sensing | Resources for<br>OCP | Resources for<br>OVP |

|--------------|----------|----------------------------------|----------------------|----------------------|

| First motor  | 3shunt   | OPAMP1+ADC1<br>OPAMP2+ADC2       | COMP1+2+3            | COMP7 + ADC1         |

| Second motor | 3shunt   | OPAMP3+ADC3<br>OPAMP4+ADC4       | COMP4+5+6            | ADC1                 |

| Motor        | Тороlоду | Resources for<br>current sensing | Resources for<br>OCP | Resources for<br>OVP |

|--------------|----------|----------------------------------|----------------------|----------------------|

| First motor  | 1shunt   | ADC2                             | COMP1                | ADC1                 |

| Second motor | 3shunt   | OPAMP3+ADC3<br>OPAMP4+ADC4       |                      | ADC1                 |

## PGA, dual 3shunt with shared resources

- On top of this, an additional (optional) configuration of F3's resources has been dedicated to the dual 3shunt case

- The default choice assigns 4 OPAMP/ADC, i.e. 2 OPAMP/ADC for each motor

- The optional "Shared resource option" assigns 2 OPAMP/ADC in total, namely OPAMP1/ADC1 + OPAMP3/ADC3, sparing 2 OPAMP/ADC for other purposes

- The pinout assignment is fixed:

| Control Stage - Analog Input a                                                                                                 | nd Protection                                                                           |                                                            |                                                  |                                  | at and thotection                                        |                                                   |                                  |

|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------|----------------------------------|----------------------------------------------------------|---------------------------------------------------|----------------------------------|

| Motor 1 Phase current feedback                                                                                                 | Motor 2 Phase current feedb                                                             | ack Bus voltage feedb                                      | ack Temperature feedb                            | ack PFC stage feedback           | ack Motor 2 Phase                                        | current feedback Bu                               |                                  |

| Embedded PGA     External OPAMP                                                                                                | OCP Topo (Both motors)<br>Embedded HW OCP<br>External Protection<br>No protection       | Configuration Shared resources                             | for both motors                                  |                                  |                                                          |                                                   |                                  |

| Sensing<br>Setting<br>Sampling Time<br>Sampling Time<br>Maximum modulation<br>Peripheral Selection                             | 7.5         ADC clk           417         ns           94         %           ADC1/ADC3 | Pin map<br>Ch phase U<br>Ch phase V<br>Ch phase W          | ADC1_IN3 (A2)<br>ADC3_IN1 (B1)<br>ADC12_IN6 (C0) |                                  | Pin map<br>Ch phase U<br>Ch phase V<br>Ch phase W        | ADC1_IN3 (A2)<br>ADC3_IN1 (B1)<br>ADC34_IN7 (D10) |                                  |

| Sensing OPAMP<br>Setting<br>Peripheral selection<br>OPAMP Gain<br>Int gain type<br>Overall Network Gain<br>Vout (polarization) | OPAMP1/OPAMP3                                                                           | Pin map<br>Not inverting<br>Ch U A5<br>Ch V A7<br>Ch W B13 | OPAMP1 A3<br>OPAMP3 B2                           | Output<br>OPAMP1 A2<br>OPAMP3 B1 | Ph map<br>Not inverting<br>Ch U A1<br>Ch V A3<br>Ch W B0 | OPAMP1 A3<br>OPAMP3 B10                           | Output<br>OPAMP1 A2<br>OPAMP3 B1 |

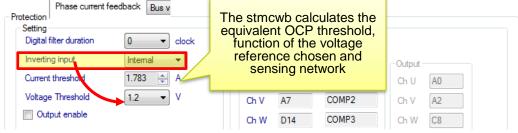

#### Comparators 65 WB settings

| Current Protection Topology     Embedded HW OCP     External Protection     No protection |                                 |  |

|-------------------------------------------------------------------------------------------|---------------------------------|--|

| Phase current feedback Bus v<br>Setting<br>Digital filter duration 0 - clock              | Pin map<br>Inverting input none |  |

| Inverting input Internal -                                                                | Not inverting Output            |  |

| Current threshold 1.783 🚔 A                                                               | Ch U A1 COMP1 Ch U A0           |  |

| Voltage Threshold 1.2 V                                                                   | Ch V A7 COMP2 Ch V A2           |  |

| Output enable                                                                             | Ch W D14 COMP3 Ch W C8          |  |

| - Pr | otection          | edback  | Bus voltage feedback | Temper  | [              |      |       |

|------|-------------------|---------|----------------------|---------|----------------|------|-------|

|      | Setting           |         |                      | - Pin m | пар            |      |       |

|      | Embedded HW C     | OVP     |                      | Not     | inverting comp | A0 - | COMP7 |

|      | Inverting input   | In      | temal 🔻              | Inve    | erting input   | none |       |

|      | Voltage threshold | 15      | i0 🚔 V               | Outp    | put comp pin   | C2 🔻 |       |

|      | Comparator input  | 1.      | 2 🗸 V                |         |                |      |       |

|      | On over voltage   | Disable | PWM generation 👻     |         |                |      |       |

|      | Output enable     |         |                      |         |                |      |       |

|      |                   |         |                      |         |                |      |       |

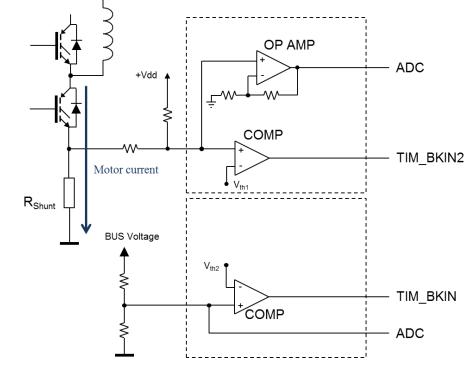

## Overcurrent protection with embedded comparators

- The MC library v5.x allows F3's embedded comparators to serve as overcurrent protection (OCP) in 3shunt or 1shunt topologies.

- If both PGA for current sensing and embedded comparators for OCP are enabled, the resulting pin-out assignment is very convenient because same pins are used for both functions. Example in a 1shunt topology:

- Comparators can also be enabled in a configuration with external opamps

- On the other hand, the MC library doesn't allow to mix embedded and external comparators

## Overcurrent protection with embedded comparators

- Three different ways to set the OCP threshold:

- Internal voltage references, sparing a I/O pin, but coarse definition

• External voltage reference, 1 I/O pin (PA4), fine definition

| tection<br>Setting<br>Digital filter duration | 0 v clock  | equi<br>fui | ivalent O  | CP th<br>the e | xternal |        |    |

|-----------------------------------------------|------------|-------------|------------|----------------|---------|--------|----|

| Inverting input                               | External 🔻 | vo          | oltage ref | ereno          | ce and  | Output |    |

| Current threshold                             | 2.035 🚔 A  | 1           | e e nem g  |                | •       | Ch U   | A2 |

| Voltage Threshold                             | ▶1.24 🚔 V  | _           | Ch V D     | 12 🔻           | COMP5   | Ch V   | C7 |

| Output enable                                 |            |             | Ch W C1    | •              | COMP7   | Ch W   | C2 |

• DAC channel, 1 I/O pin (to be defined in the DAC dialog window), fine definition

| 0 v clock | The stmcwb calculates the |                                                                                           |                                                                                                        |

|-----------|---------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| DAC 🔻     |                           | Output -                                                                                  |                                                                                                        |

| 1.783 🚔 A | the desired current       | Ch U                                                                                      | A2                                                                                                     |

| 1.20 🚔 V  | threshold                 | Ch V                                                                                      | C7                                                                                                     |

|           | Ch W C1                   | Ch W                                                                                      | C2                                                                                                     |

|           | DAC ▼<br>1.783 ♀ A        | DAC Voltage reference to<br>be generated, function of<br>the desired current<br>threshold | DAC Voltage reference to<br>be generated, function of<br>the desired current<br>threshold Ch U<br>Ch V |

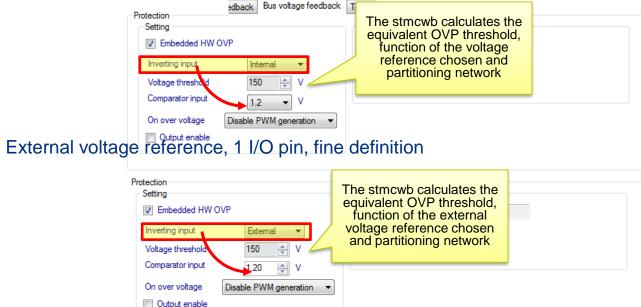

## Overvoltage protection with embedded comparators

- Three different ways to set the OVP threshold:

- Internal voltage references, sparing a I/O pin, but coarse definition

DAC channel, 1 I/O pin (to be defined in the DAC dialog window), fine definition

| Protection<br>Setting                  | <b>P</b>                                              |  |

|----------------------------------------|-------------------------------------------------------|--|

| Embedded HW OVP                        | The stmcwb calculates the                             |  |

| Inverting input  DAC                   | DAC voltage reference to<br>be generated, function of |  |

| Voltage threshold                      | the desired voltage                                   |  |

| Comparator input 1.20 🐑 V              | threshold                                             |  |

| On over voltage Disable PWM generation | ·                                                     |  |

| Output enable                          |                                                       |  |

•